Gold Standard PCIe Retimer Portfolio

Field-tested and widely deployed at all major hyperscalers & AI platform providers

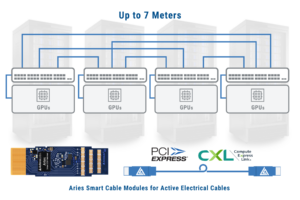

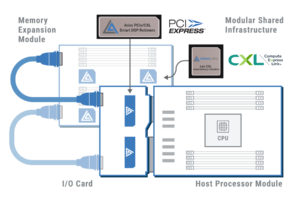

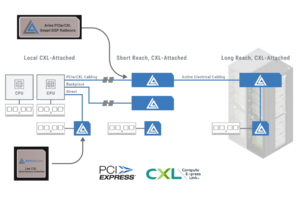

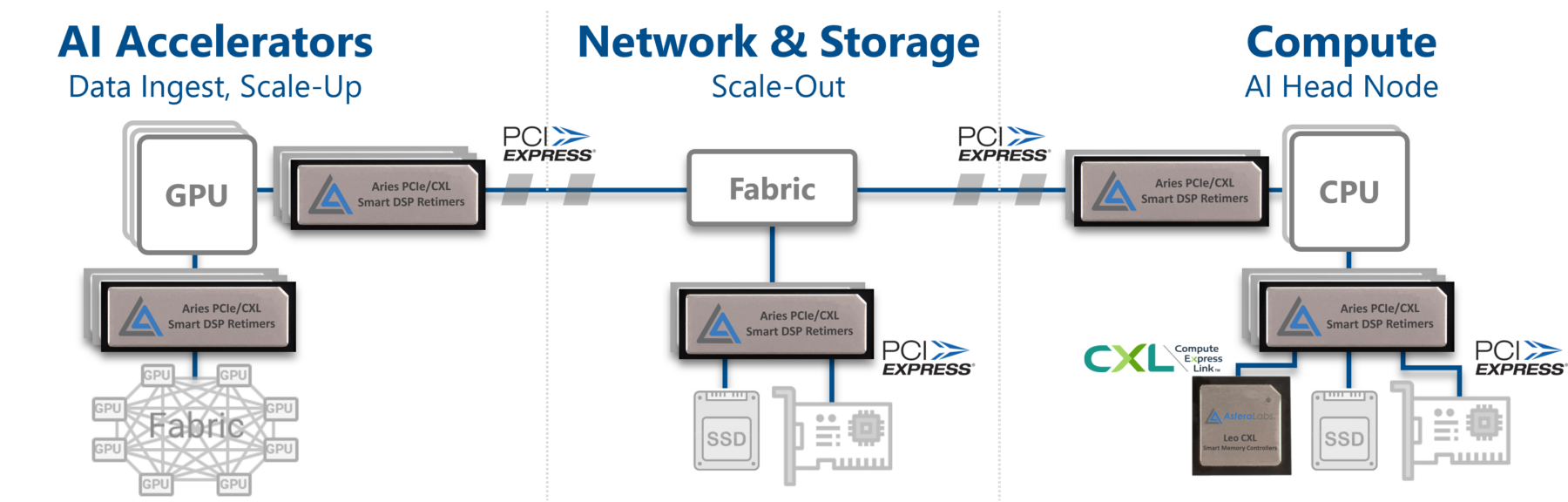

- Solves high-speed PCIe/CXL signal integrity challenges in AI and general purpose servers with reliable 3x reach extension

- Purpose-built for AI and cloud infrastructure delivering high performance, low power, and seamless interoperability

- Provides a smart connectivity backbone that is reliable, scalable and customizable for diverse cloud-scale deployments

- Comprehensive solution complete with

software suite for advanced Link, Fleet & RAS telemetry & diagnostics

software suite for advanced Link, Fleet & RAS telemetry & diagnostics

Aries 6 Highlights

Seamless upgrade from 2nd generation Aries 5 utilizing industry standard footprints

Lowest power PCIe 6.x Retimer

11W typical

Optimizes cloud infrastructure TCO &

simplifies system design

Robust signal integrity

36dB 64GT/s PAM4

SerDes and DSP customized for

demanding AI server channels

Why AI & Cloud Providers Use the Aries Retimer Portfolio

Enhanced portfolio with years of learnings from cloud-scale deployments

Robustness

Enhanced Signal Integrity: Proven track record of solving high-speed PCIe/CXL signal integrity challenges with reliable 3x reach extension

Optimized Thermal Efficiency: Low power Retimers with integrated heat spreader simplify platform thermal design and cooling while reducing infrastructure TCO

Rigorous Interop Testing: System testing with major hosts and 50+ endpoints in our Cloud-Scale Interop Lab minimizes interoperation risk and accelerates time-to-market

Ease-of-Use

Simple Board Design: Small package footprint with integrated AC coupling caps and flexible clocking modes simplify routing and reduce solution size

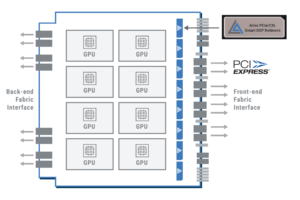

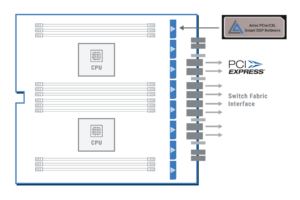

Comprehensive Retimer Portfolio: Multiple packages (8/16 lane), protocols (PCIe/CXL) and form factors (ICs/Smart Cable Modules/boards) for diverse AI & cloud

SW-defined Architecture: COSMOS with Aries software-defined architecture adjusts protocol and state transitions to support open and diverse PCIe ecosystem

Fleet Management

Quick Debug: Built-in protocol analyzer with link state history and timestamps, real-time eye scan and RX lane margining accelerate development and debug

Deep Diagnostics: Real-time lane, link, and device health monitoring help identify system-level issues before they affect customers and improve data center uptime

In-field Upgrade: COSMOS software upgrades enable seamless deployment of new features into existing infrastructure in the field

Videos

Connectivity Enriches Our Connections

See how our semiconductor-based connectivity solutions are transforming the future of AI.

Orderable Information

Aries PCIe/CXL Smart DSP Retimers

| Orderable Part Number | Documents | Retimer Generation | Max PCIe Gen | PCIe Lanes | Ordering | Status |

|---|---|---|---|---|---|---|

| PT6082LR | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Smart_DSP_Retimer_Family-Product_Brief.pdf | 3rd | PCIe 6.x | x 8 | Contact Us, https://www.asteralabs.com/product-details/PT6082LR/ | Sampling |

| PT6082LX | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Smart_DSP_Retimer_Family-Product_Brief.pdf | 3rd | PCIe 6.x / CXL 3.x | x 8 | Contact Us, https://www.asteralabs.com/product-details/PT6082LX/ | Sampling |

| PT6162LR | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Smart_DSP_Retimer_Family-Product_Brief.pdf | 3rd | PCIe 6.x | x 16 | Contact Us, https://www.asteralabs.com/product-details/PT6162LR/ | Sampling |

| PT6162LX | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Smart_DSP_Retimer_Family-Product_Brief.pdf | 3rd | PCIe 6.x / CXL 3.x | x 16 | Contact Us, https://www.asteralabs.com/product-details/PT6162LX/ | Sampling |

| PT5082LR | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Smart_DSP_Retimer_Family-Product_Brief.pdf | 3rd | PCIe 5.0 | x 8 | Contact Us, https://www.asteralabs.com/product-details/PT5082LR/ | Sampling |

| PT5082LX | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Smart_DSP_Retimer_Family-Product_Brief.pdf | 3rd | PCIe 5.0 / CXL 2.0 | x 8 | Contact Us, https://www.asteralabs.com/product-details/PT5082LX/ | Sampling |

| PT5162LR | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Smart_DSP_Retimer_Family-Product_Brief.pdf | 3rd | PCIe 5.0 | x 16 | Contact Us, https://www.asteralabs.com/product-details/PT5162LR/ | Sampling |

| PT5162LX | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Smart_DSP_Retimer_Family-Product_Brief.pdf | 3rd | PCIe 5.0 / CXL 2.0 | x 16 | Contact Us, https://www.asteralabs.com/product-details/PT5162LX/ | Sampling |

| PT5081LR | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Smart_DSP_Retimer_Family-Product_Brief.pdf | 2nd | PCIe 5.0 | x 8 | Contact Us, https://www.asteralabs.com/product-details/PT5081LR/ | Production |

| PT5081LX | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Smart_DSP_Retimer_Family-Product_Brief.pdf | 2nd | PCIe 5.0 / CXL 2.0 | x 8 | Contact Us, https://www.asteralabs.com/product-details/PT5081LX/ | Production |

| PT5161LR | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Smart_DSP_Retimer_Family-Product_Brief.pdf | 2nd | PCIe 5.0 | x 16 | Contact Us, https://www.asteralabs.com/product-details/pt5161lr/ | Production |

| PT5161LX | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Smart_DSP_Retimer_Family-Product_Brief.pdf | 2nd | PCIe 5.0 / CXL 2.0 | x 16 | Contact Us, https://www.asteralabs.com/product-details/pt5161lx/ | Production |

| PT4080LR | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Smart_DSP_Retimer_Family-Product_Brief.pdf | 1st | PCIe 4.0 | x 8 | Contact Us, https://www.asteralabs.com/product-details/pt4080lr/ | Production |

| PT4161LR | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Smart_DSP_Retimer_Family-Product_Brief.pdf | 1st | PCIe 4.0 | x 16 | Contact Us, https://www.asteralabs.com/product-details/pt4161lr/ | Production |

Evaluation Kits

| Evaluation Kit | Image | Documents | Description | Max PCIe Gen | PCIe Lanes | Pack Quantity | Ordering | Production Status |

|---|---|---|---|---|---|---|---|---|

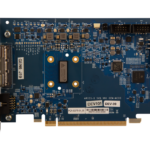

| Equinox 6 PCIe 6.x Riser Card |  | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Equinox_6_Retimer_CEM_AIC-Product_Brief.pdf | Aries 6 Smart Retimer CEM-CEM Add-in-Card | PCIe 6.x | x 16 | 1 | Contact Us, https://www.asteralabs.com/products/smart-retimers/pcie-cxl-smart-retimers/order-systems/?system=EQUINOX-6 | Sampling |

| Solstice 6 PCIe 6.x Riser Card |  | https://www.asteralabs.com/wp-content/uploads/2024/03/2402_Astera_Labs-Aries_Solstice_6_Retimer_MCIO_AIC-Product_Brief.pdf | Aries 6 Smart Retimer CEM-MCIO Add-in-Card | PCIe 6.x | x 16 | 1 | Contact Us, https://www.asteralabs.com/products/smart-retimers/pcie-cxl-smart-retimers/order-systems/?system=SOLSTICE-6 | Sampling |

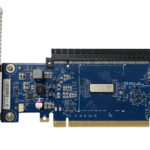

| Equinox 5 PCIe 5.0 Riser Card |  | https://www.asteralabs.com/wp-content/uploads/2020/11/Astera_Labs_Eclipse_Equinox_Product_Brief.pdf | Aries 5 Smart Retimer CEM-CEM Add-in-Card | PCIe 5.0 | x 16 | 1 | Digi-Key, https://www.digikey.com/en/products/detail/astera-labs-inc/EQUINOX-REVA/13982648?s=N4IgTCBcDaIKYEcCuBLAdgewB4gLoF8g; Contact Us, https://www.asteralabs.com/products/smart-retimers/pcie-cxl-smart-retimers/order-systems/?system=EQUINOX-REVA | Production |

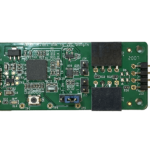

| COMET-REVA |  | https://www.asteralabs.com/wp-content/uploads/2020/08/Astera_Labs_COMET_Product_Brief.pdf | Astera Labs USB-to-I2C Communication Module | 1 | Digi-Key, https://www.digikey.com/en/products/detail/astera-labs-inc/COMET-REVA/13881175?s=N4IgTCBcDaIMYHsC2BTALgAgIYGc0oCcsMAbLAIxxAF0BfIA; Mouser, https://www.mouser.com/ProductDetail/Astera-Labs/COMET-REVA?qs=%2Fha2pyFadujscaAy75Pb6mldQROydX7z1bYmIMd%252Bpx6QoUJRZnAUzA%3D%3D; Contact Us, https://www.asteralabs.com/order-products/?product=COMET-REVA | Production |

You may also order from our distributors >